Статья описывает разработку микроархитектуры аппаратного вычислителя для нейронной сети, способной распознавать простые фигуры. В качестве языка реализации выбран SystemC, позволяющий моделировать аппаратные особенности системы.

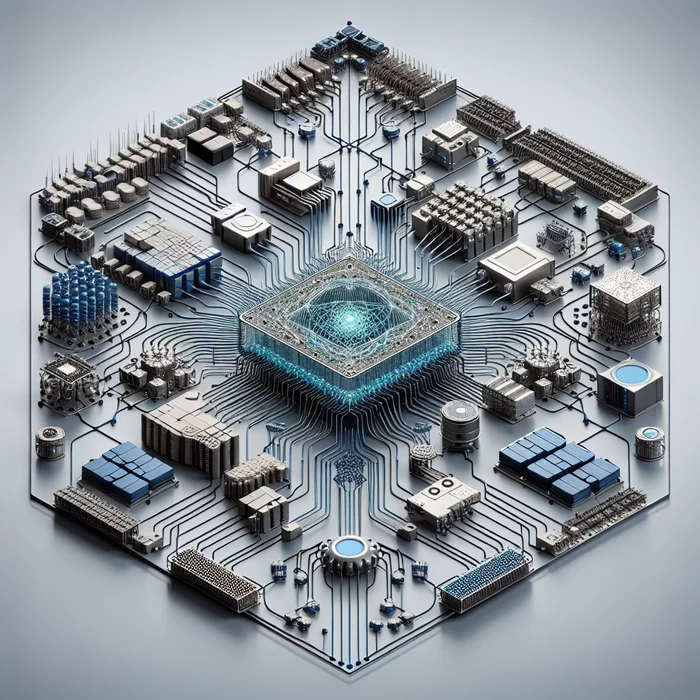

Предложенная архитектура состоит из независимых ядер для вычислений, управляющего модуля, ядра активации, общей памяти и контроллера ввода-вывода. Ядра вычисляют взвешенные суммы, а активация вынесена в отдельный блок для экономии ресурсов и возможности замены функции активации. Управляющий модуль отвечает за загрузку данных и запуск вычислительных ядер.

Микроархитектура вычислительного ядра включает очереди входов и весов, умножители и сумматор. Для реализации блока активации используется таблица значений, аппроксимирующая функцию линейными участками.

Модель ускорителя на SystemC включает модули для активации, управления, ввода-вывода, общей памяти и вычислительных ядер. Коммуникация устройств упрощена через прямые соединения. Результаты моделирования показали, что основное время уходит на загрузку данных, а не на вычисления. В дальнейшем планируются более детальные статьи, посвященные узким местам и оптимизации.

Изображение носит иллюстративный характер

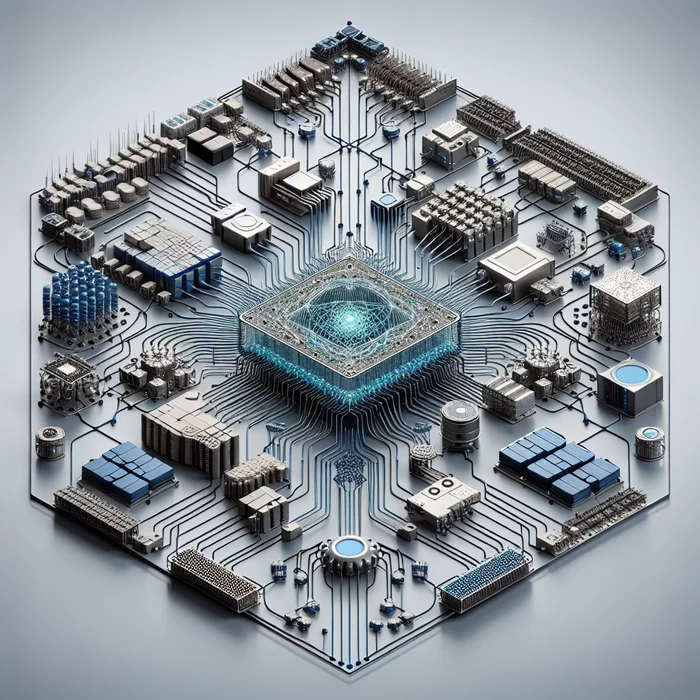

Предложенная архитектура состоит из независимых ядер для вычислений, управляющего модуля, ядра активации, общей памяти и контроллера ввода-вывода. Ядра вычисляют взвешенные суммы, а активация вынесена в отдельный блок для экономии ресурсов и возможности замены функции активации. Управляющий модуль отвечает за загрузку данных и запуск вычислительных ядер.

Микроархитектура вычислительного ядра включает очереди входов и весов, умножители и сумматор. Для реализации блока активации используется таблица значений, аппроксимирующая функцию линейными участками.

Модель ускорителя на SystemC включает модули для активации, управления, ввода-вывода, общей памяти и вычислительных ядер. Коммуникация устройств упрощена через прямые соединения. Результаты моделирования показали, что основное время уходит на загрузку данных, а не на вычисления. В дальнейшем планируются более детальные статьи, посвященные узким местам и оптимизации.